| |

|

| 网络化IP核 > IRIGtimeM: IRIG-B主站IP核 |

|

| |

IRIGtimeM: IRIG-B主站IP核 |

|

|

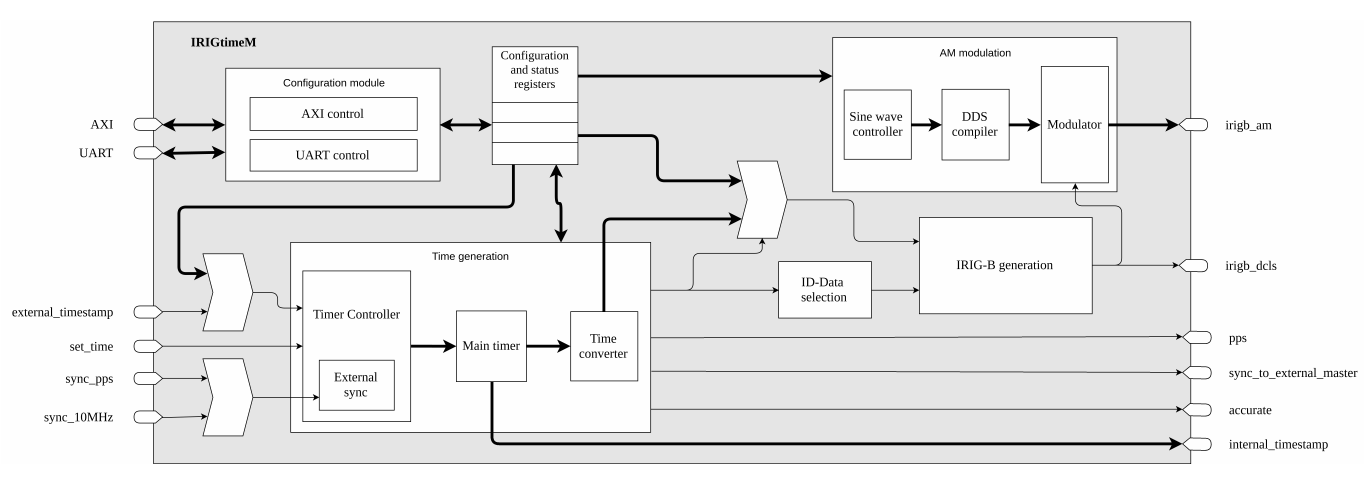

IRIGtimeM 在FPGA器件上实现兼容IRIG 200-04的时间同步主站。该IRIG-B主站IP旨在支持所有IRIG-B编码表达式以及DCLS和AM调制,以提供最大的灵活性。

此IRIG-B主站IP每秒生成IRIG-B帧,包括必选和可选的时间信息(秒、分钟、小时、天、年、控制功能和连续二进制秒数),具体取决于配置上所选择的IRIG-B时间代码。该IP被设计为提供自主操作,需要尽可能少的配置。

以下Xilinx FPGA系列支持IRIG timeM:

- 6系列(Spartan,Virtex)

- 7系列(Zynq,Spartan,Artix,Kintex,Virtex)

- Ultrascale(Kintex,Virtex)

- Ultrascale +(Zynq MPSoC,Kintex,Virtex)

|

|

用于Xilinx Vivado工具的网管以太网交换机IP内核 |

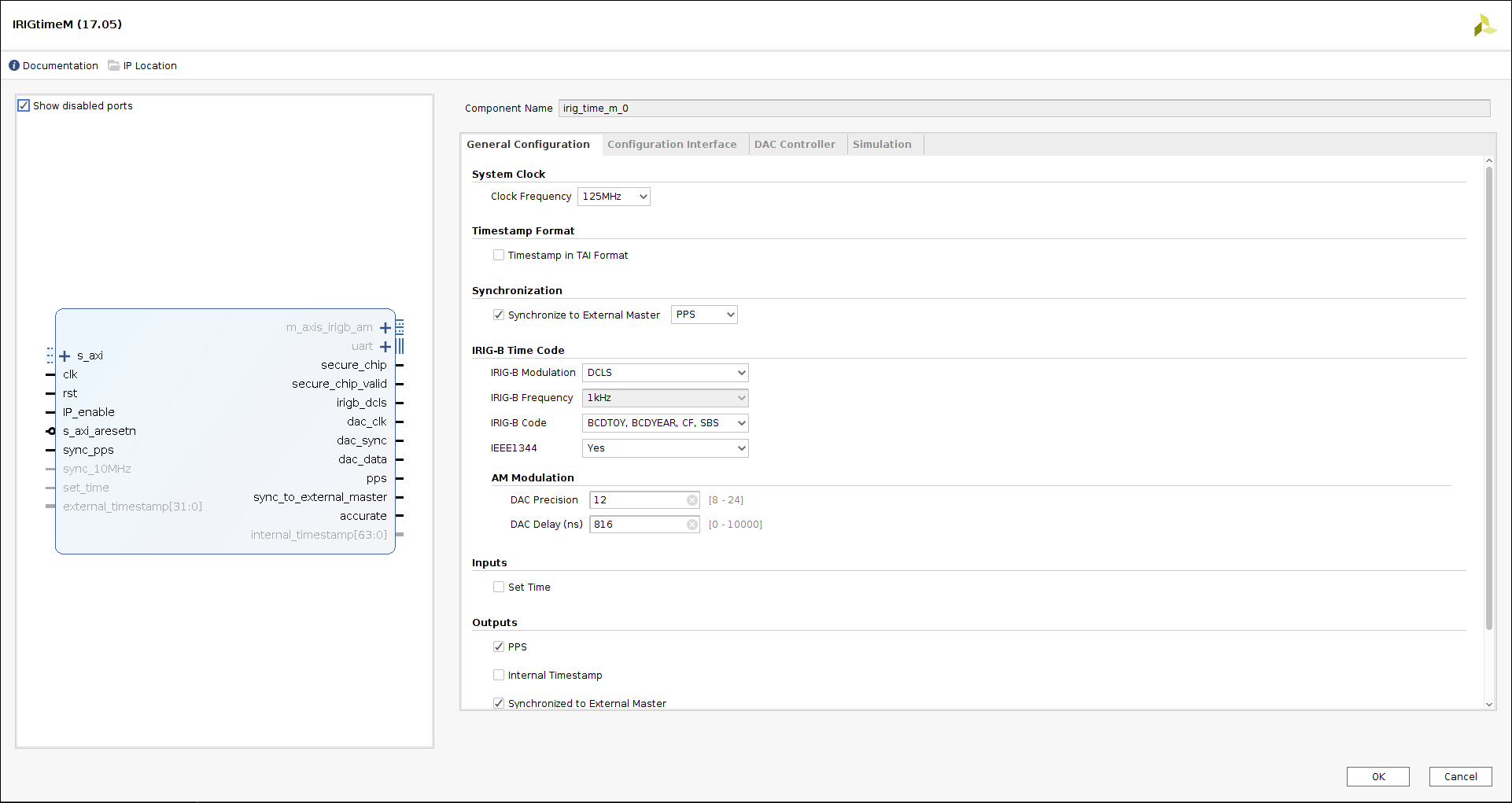

通过利用新的Xilinx Vivado工具,可以轻松地将其集成到你的FPGA设计中,该工具允许在图形用户界面中使用IP内核,并以简便的方式配置IP参数。

IRIGtimeM 主要特点:

- 符合IRIG 200-04的时间同步主站

- 支持DCLS和AM调制

- 支持所有IRIG-B编码表达式,包括年份信息、控制功能和直线二进制秒

- 输出类型(IRIG-B时间码)可在实施前和运行中配置

- 精确的IRIG-B输出,以提供纳秒级精度

- IP初始设置的32位时间戳输入

- 定期脉冲输出用于测试

IRIGtimeM IP内核框图如下图所示:

参考设计支持的板:

欲了解更多信息,请联系我们:info@hkaco.com。 |

|

|

| |

|

|

| |

关于虹科:虹科积极进取,不断探索科技新领域。最优秀的员工和最好的技术能够接受最困难的挑战。为您找到最佳解决方案。虹科靠口碑赢得客户。

广州 400 999 3848 | 上海 021-6728 2707 | 北京 010-5781 5068 | 西安 029-8187 3816 | 成都 028-6391 0020

深圳 0755-2267 7479 | 武汉 027-8193 9100 | 香港 6749 91599 | 台湾 901299121

sales@hkaco.com | 广州虹科电子科技有限公司 | 广州科学城润慧科技园

|

|