GigaView

Nowadays digital devices have become more complex, more sensitive to signal quality and harder to debug including high-frequency buses and high speed logic families.

Debugging digital hardware can be a difficult and long operation because new effects caused by fast edges like logic errors, crosstalk, ground bounce and power distribution artifacts can occur.

Timing error debugging includes the characterization of the following problems:

- Glitches

- Setup/Hold Violations

- Timing Margin Verification

- Crosstalk/ Jitter Analysis

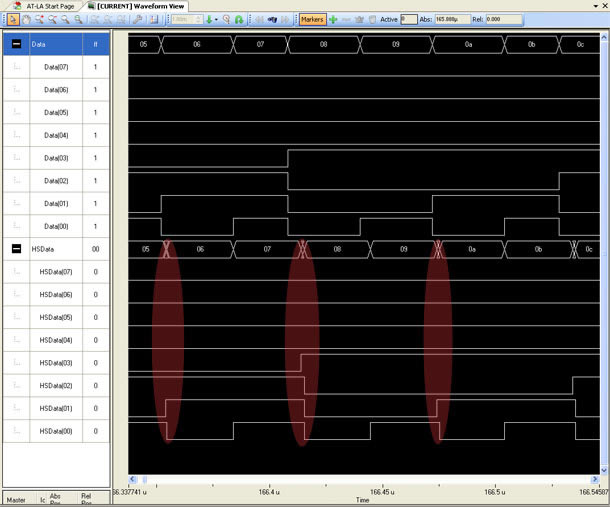

Thanks to the GigaView technology the AT-LA500 is capable of performing timing error debugging despite of general purpose logic analyzers that are traditionally unable to perform such kind of analysis. The GigaView technology provides a 2ns timing resolution with up to 4 MSamples depth simultaneouslywith a 666 ps high resolution timing within the same acquisition and using the same probes.

It is like performing two analysis in one: a deep timing analysis and an additional high-resolution timing analysis.

Glitches

Glithches are usually very narrow pulses that can be very difficult to detect, capture and hard to resolve. Their effect are often unpredictable and they can be the first sign of device faults like driver errors, timing violations and crosstalk.

AT-LA500 deep timing signal waveform ( 2ns resolution and up to 4 MSamples memory depth) can examine all the signal lines of the bus at once and look for events or faults; after a particular event, like a glitch, has been detected, the GigaView waveforms can display all the channels in high resolution (666 ps) with 1024 samples depth per channel, providing the way to examine the event in detail.

GigaView high-resolution timing window is able to reveal glitches and to measure their duration with high accuracy.

Setup/Hold Violations

Setup/Hold parameter is a common source of digital system errors and its analysis can be difficult with the traditional approach of probing a clock and a data line using a oscilloscope.

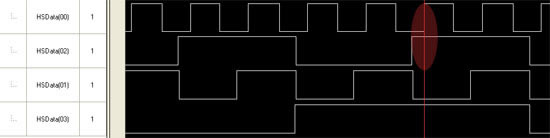

The logic analyzer approach can monitor simultaneously every signal in the system for detecting setup/hold violations and when a problem is discovered in a particular time window, the AT-LA500GigaView can measure in that window setup/hold times with an accuracy of 666 ps.

Timing Margin Verification

666 ps resolution on all channels with a maximum skew of 666 ps from channel to channel, allows designers to move from simply troubleshooting apparent problems to actually verifying the timing margins of their designs. Sample points can be moved in 666 ps increments to precisely determine setup-and-hold windows and examine the behavior of clocks, data and address lines with respect to each other, and asynchronous inputs.

AT-LA500数字码型发生器 - 取样器 >

Email 本页 Email 本页

需要更详细资料?请通过sales@hkaco.com联系我们。

|